都灵(意大利)

9月 26, 2024

KGD测试:确保半导体制造品质

已知良好芯片(Known Good Die, KGD)测试是半导体制造过程中的一个关键步骤,尤其是对于像碳化硅(SiC)器件这样的功率半导体器件。通过在单个芯片级别进行全面测试,制造商可以在封装前识别和消除缺陷组件,从而确保其产品的整体质量和可靠性。

半导体制造中的多层测试方法:晶圆、芯片和封装测试

半导体制造是一个复杂的过程,需要在各个阶段进行细致的测试,以确保设备功能无瑕。测试阶段包括:

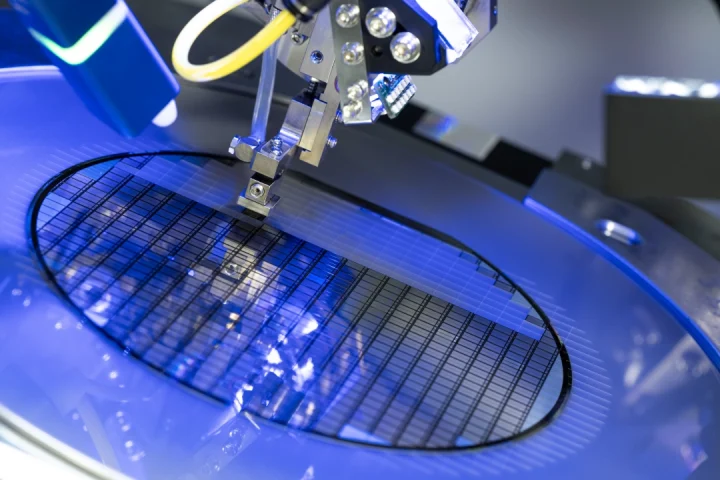

晶圆测试

- 在制造过程的早期进行,通常在关键层沉积和图案化到硅晶圆上之后。

- 使用专用设备(带有探针卡的晶圆探针台)来探测晶圆上的单个电路,并评估基本功能和电特性。

- 作为初步筛选步骤,用于在进一步处理前识别和移除有重大缺陷的晶圆。

芯片测试(KGD)

- 专注于从晶圆上通过切割工艺分离出来的单个芯片。

- 使用专用处理器和探测模块来移动和探测芯片。

- 对于确保功率半导体的可靠性至关重要,允许进行在晶圆级别无法进行的测试。

封装测试

- 在芯片被封装在最终的保护包中并与外部连接后进行。

- 验证整个封装设备的功能,包括芯片与封装材料之间的相互作用。

- 这一最终测试确保完整设备在发货给客户前满足所有性能规格。

通过实施包含晶圆、KGD和封装测试的多层测试方法,制造商可以对其半导体设备的质量和可靠性达到高度信心,优化产量并降低制造成本。通过在从原始硅晶圆到完成模块的各个阶段筛选部件,可以尽早识别和移除缺陷组件。

KGD测试对功率半导体器件的重要性

KGD测试阶段为功率半导体器件提供了几个关键优势:

- 早期缺陷检测:在封装前识别和移除缺陷芯片显著减少了产量损失和下游成本。早期发现缺陷最大限度地减少了资源浪费:在单片晶圆上发现缺陷芯片的成本远低于在完全组装的模块中发现问题的成本。

- 更快的上市时间:早期识别和解决问题防止了因晚期发现缺陷和返工造成的延迟。

- 增强的可靠性:KGD测试有助于确保只有高质量组件用于最终模块,从而提高可靠性和性能。

- 改进的工艺:KGD测试数据可用于识别制造过程中的潜在弱点,并进行必要的调整。

揭示KGD测试的力量:SiC器件的静态、动态和短路测试

虽然KGD测试提供了显著优势,但它也带来了独特的挑战。与硅器件不同,SiC在更高的电压和电流下运行。这需要使用能够安全、准确地处理这些极端条件的专用测试设备,包括晶圆、KGD和封装级别。

在KGD阶段进行的具体测试,用于识别和消除潜在缺陷,可以大致分为三类:

静态测试

这些测试在稳态条件下测量SiC器件的基本电参数。

- SiC器件的常见静态测试包括:

- 阈值电压(Vth):测量打开设备所需的最小栅极电压。

- 导通电阻(Ron):表征设备导电时的电阻。

- 泄漏电流(Ileak):评估设备在关闭状态时流过的电流量。

- 击穿电压(Vbr):确定设备在发生击穿前能承受的最大电压。

动态测试

这些测试评估SiC设备在模拟现实使用案例的动态操作条件下的行为:

- SiC器件的关键动态测试包括:

- 开关特性:测量设备在导通和关断状态之间转换所需的时间,包括导通时间、关断时间和栅极电荷特性。

- 转移函数:分析栅极电压与漏极电流之间的关系,提供设备在开关期间的行为洞察。

- 电容-电压(C-V)测量:评估设备在不同栅极电压下的电容,有助于识别栅极氧化物层中的潜在缺陷。

短路测试

- 这个关键测试评估SiC设备承受突然且显著增加的电流流动的能力。

- 它模拟了设备在其端子之间经历短路的潜在故障条件。

- 短路测试测量设备失效所需的时间(短路承受时间),并有助于识别可能导致正常操作期间灾难性失败的隐藏缺陷。

通过实施包含这些静态、动态和短路测试的全面KGD测试策略,制造商可以有效地筛选出缺陷SiC设备。这不仅确保了最终产品的可靠性和性能,还通过最小化产量损失来降低生产成本。

短路测试的挑战

与具有集成散热器的封装模块不同,KGD设备体积小、薄,并且缺乏专门的散热机制。在短路测试期间,高电流流动产生大量热量,很容易超过设备的热容量并导致灾难性故障。由于SiC的有限散热和易碎性,KGD级别的严重短路事件可能导致爆炸。这构成了安全隐患,并可能损坏测试设备。KGD短路测试期间的高温和爆炸风险可能导致设备金属化粘附到探测针脚上。这给进一步测试中的设备移除带来了挑战,并向测试设备中引入了污染风险,影响未来测试的准确性。

安全、有效的KGD短路测试设备的必备功能

对KGD SiC设备进行安全和有效的短路测试需要配备几个关键功能的专用测试设备。安全的一个关键要素是在发生过电流事件时能够在非常短的时间内(数十纳秒)中断电流流动。这种快速关断有助于防止在KGD短路测试期间产生过多的热量和潜在的爆炸。实现这种超快速电流关断能力需要先进的电子组件和高速电路设计。

在测试路径中最小化杂散电感也是进行准确和可控短路测试的关键。杂散电感可以减慢电流脉冲的上升和下降时间,影响测试结果,并可能在发生故障时延迟电流关断。测试设备设计应使用低电感组件,并最小化电缆长度,以减少电路中的总体杂散电感。

除了过电流保护外,测试器还应包含防止过电压情况的保障措施。这有助于防止设备损坏和测试期间可能发生的电弧事件。可以使用电压监测电路和快速动作继电器来检测过电压条件,并在必要时断开电源。

最后,必须仔细评估电弧抑制的风险。在短路测试期间,电流流动的突然和显著增加可以导致周围气体分子的电离。这在设备端子之间创建了一条导电路径,导致产生电弧。电弧产生强烈的热和光,可能损坏正在测试的KGD设备,甚至损坏测试设备。根据帕邢定律(描述气体击穿电压(引发电弧所需的电压)、气体压力和两个导体之间间隙长度的关系),使用压缩空气调节测试室是抑制SiC设备KGD短路测试期间电气电弧的关键策略。通过增加测试室中气体的压力,我们有效地提高了击穿电压:这使得即使在短路测试的高电流条件下,也更难在设备端子之间引发电弧,从而保护设备和测试设备。在测试室中使用干空气可最大限度地减少水蒸气的存在,进一步有助于电弧抑制。

通过纳入这些必备功能,KGD短路测试设备可以在安全性、有效性和识别SiC设备潜在弱点的能力之间实现平衡。

KGD测试的电流保护模块:保护接触探针

在KGD测试期间,尤其是在短路测试中,可能会出现高电流流动。这可能会损坏用于探测SiC设备的精密接触探针。SPEA的测试设备配备了一个电流保护模块,作为保障措施,限制可以通过探针流动的电流。这防止了过多的热量产生和探针可能的熔化或变形,确保了其使用寿命和功能。

电流保护模块的有效性进一步通过其能够根据所用接触探针的具体电流承载能力进行调整而得到增强。这确保了电流限制设置得当,以保护探针而不影响测试本身。

在KGD测试设置中,接触探针(探针针脚或针头)通常分组以探测SiC设备的不同部分。电流保护模块可以通过允许在这些不同组之间平衡电流来提供额外的好处。这一功能对于确保测试期间电流流动在设备上均匀分布至关重要。电流分布不均可能导致测试结果不准确或甚至损坏设备的特定区域。

结论

已知良好芯片(KGD)测试是SiC器件质量控制的基石,确保产品可靠、高性能,同时通过早期缺陷检测最小化产量损失。全面的测试策略应涵盖静态、动态和短路测试,以在真实条件下验证关键参数。

与封装模块不同,KGD设备在动态和短路测试中呈现出独特的挑战。其有限的散热能力可能导致安全隐患、爆炸和严重的设备损坏。为了减轻这些风险,测试设备应包括超快速电流限制、低杂散电感设计和电气电弧抑制机制。

通过实施这些功能,制造商可以提高其针对SiC设备的KGD测试策略的效率和有效性。